2016 的 SSD 技術即將迎來重大變化。

先前 Toshiba 與 Sandisk 公開了技術合作的 48 層 BiCS 3D NAND Flash 設計,隨後另一組有著深厚合作關係的人馬 Intel 與 Micron 也透漏了自家的 3D NAND 設計的更多資料。

其實去年底 Intel 就已經粗淺的透露了一部分的參數,包含了會具有 32 層堆疊、可提供 MLC 顆粒 256Gb(32GB)、TLC 384Gb(48GB)的容量等,現在他們透露了更多。

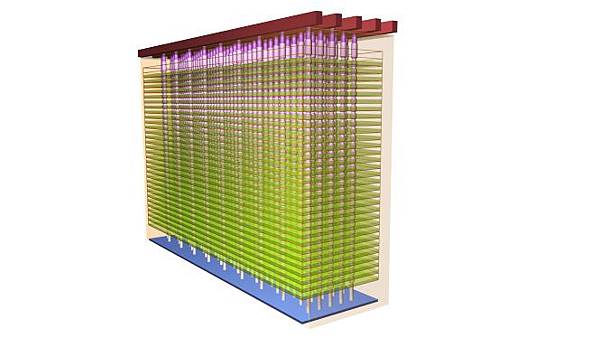

首先,新的 NAND Flash 的設計上將會具有 4 個 Plane,Plane 是整個 NAND Flash 體系中第二大的單位,僅次於 die;再下去則是我們所知道的 Block 與 Page 這些更基本的單位,設計 Plane 的用意是用來對 Block 進行劃分,相異的 Plane 是可以同時進行動作的,若少了 Plane 設計,在 Die 內就一次就只能對一個 Page 進行讀寫而降低性能,而 Intel-Micron 使用了 4 planes 設計可以有效地增加吞吐量。

在耐久性的部分,Intel 與 Micron 公開資料顯示,電荷的數量將可以回到過去平面式設計在 50 nm 左右的等級,而電荷的數量會將會影響儲存單元的判斷精確度以及控制難度,這也是為何在平面式 NAND FLASH 舊制程產品的 P/E Cycle 較高的因素。不過 Micron 方面,目前只承認會有 3,000 P/E 的表現,但 Micron 在消費級 NAND FLASH 已經維持這個數據長達數年,因此有可能只是 Micron 提供保守估計,實際上的表現可能可以來到 10,000 P/E Cycle 以上。

另外比較特別的是,Intel-Micron 的設計還是使用了傳統的 Floating Gate,而不是 Samsung、Toshiba 所使用的 Charge Trap。他們表示,Floating Gate 的設計已經存在悠久,比起相對新的 CTF 特性更能能被很好的掌握,換句話說則是以 Intel-Micron 對 Floating Gate 技術的深入了解,做起來比較省錢。當然比起 CTF 技術可能有著更低的漏電流等好處可能也在考慮範圍之內。

上市時程方面,目前 256 Gbit 的 MLC 樣品,已經出貨給特定的合作夥伴,預計今年的下半年度就可以進入量產。因此我們也許可以在明年就可以看到使用 Intel 與 Micron 3D NAND Flash 的 SSD 產品出現在商店貨架上。

(本文由 VR-Zone 授權轉載)

留言列表

留言列表