雖然三維積體電路(3D ICs)的驅動保持了性能及形狀因子,

其被採用的時間卻一直往未來延遲。許多技術上的挑戰與基礎設施等問題

造成矽導孔(TSV)技術在3D IC的量產上持續延遲。直到這些問題被解決以前,

替代方案將持續被使用。

雖然三維積體電路(3D ICs)的驅動保持了性能及形狀因子,其被採用的時間卻一直往未來延遲。許多技術上的挑戰與基礎設施等問題造成矽導孔(TSV)技術在3D IC的量產上持續延遲。直到這些問題被解決以前,替代方案將持續被使用。

在技術面上,雖然導通孔的形成與填充已有許多進展,但是仍有一些製程步驟如晶圓薄膜化時的剝離製程,會對良率造成影響而且產速較低。問題在於複合材料與機器設備的問題。新材料正在導入中且顯示是具有前途的,但是工程是需要時間的。堆疊記憶體似乎邁出了第一步,但已證明是非常具有挑戰的。不需剝離製程的3D IC解決方案已被Tezzaron公司提出,其應用了爾必達公司在破產之前使用在堆疊記憶體上的架構和創新製程。

許多公司在它們的封裝發展藍圖上會秀出矽中介層或2.5D解決方案,其方法是把邏輯元件安裝在堆疊記憶體的旁邊,而矽導孔則是在基底層內。問題在於此方法假設有矽導孔的堆疊記憶體在成本/效能比符合需求的前提下是市場上可取得的。若無法取得堆疊記憶體,甚至將延後2.5D被使用的時程。一些公司也指出矽中介層的成本太高,它們想要考慮玻璃中介層或甚至是高密度有機底材。目前有導通孔的玻璃中介層並非商用上可取得的,而有良好特性的有基底材也還在研發中。

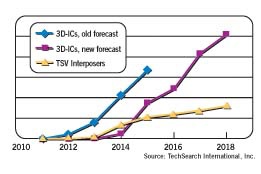

中介層對3D IC預測的影響

對於堆疊的記憶體和邏輯產業仍然需要熱感知設計工具或甚至是新的散熱解決方案給包含邏輯與記憶體的堆疊層。測試方法的開發上已經取得了進展,但還有其他工作要做。電子設計自動化( EDA)工具的商業化將對產業帶來非常大的受益。

一旦3D IC的技術挑戰被解決且技術變得有成本效益,商業的挑戰將持續直到產業決定一個模式。根據日月光( ASE)經驗,產業將依客戶與代工別而使用多種模型。

有許多達到3D封裝的方法,包括堆疊晶粒與銲線或銲線/覆晶晶片,堆疊式封裝,封裝層疊(PoP),及晶片層疊(CoC)。公司計畫繼續使用現今的3D封裝技術配合進化改善,且採用2.5D或中介層解決方案直到完成3D IC的挑戰。重要的是要記得新封裝技術的導入需要時間,且製程和基礎設施必須適當的發展:賽靈思(Xilinx)花了六年的時間研發出現在知名的場域可程式化閘陣列(FPGA),在使用TSV方案的矽中介層上分隔晶粒。SST-AP/Taiwan

資料來源:半導體科技

留言列表

留言列表