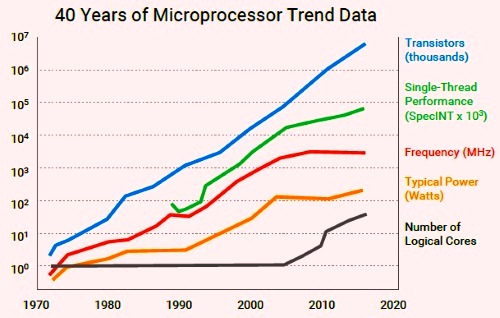

Google引述史丹佛大學(Stanford)製作的圖表,表示處理器性能進展停滯

(來源:Google)

Google的一位主管在日前於美國舉行的年度產業策略高峰會(Industry Strategy Symposium)上對與會企業高層表示,摩爾定律(Moore’s law)並未跟上仍然「年輕」的雲端服務市場之腳步,他呼籲產業界推動資料中心專用處理器、記憶體、互連與封裝等技術的創新。

「摩爾定律速度趨緩以及雲端服務的成長,已經把我們帶到了一個反曲點(inflection point);」負責資料中心硬體採購的Google資深營運總監Prasad Sabada表示:「遊戲規則又一次改變,我們需要產業界以有意義的方式來回應。」

具體來說,他呼籲推動處理器的最佳化,降低本文切換(context switching)以及其他對Google實際工作負載十分關鍵的運作之延遲:「我們已經看到許多處理器針對Spec性能評測基準進行最佳化,但是在Google,我們的工作負載與Spec大不相同。」

Google也想要更低延遲的記憶體晶片,「我們能從降低記憶體延遲取得很大的進展,就像處理器的性能提升那樣;」Sabada所指的是新一代記憶體架構的潛力表現。

在近一年前,Google的競爭對手Facebook開始支援英特爾(Intel)的3D XPoint記憶體,這種新一代記憶體在許多方面的表現號稱優於今日的NAND快閃記憶體;英特爾已經在去年底開始限量提供該記憶體晶片樣品。

在互連方面,Sabada表示,今日的典型處理器匯流排有許多針對I/O與加速器元件的overhead存取,並不適合新興的記憶體架構;此外,需要光學介面例如矽光子(silicon photonics)技術,來連結資料中心裡的伺服器。

Sabada指出IBM的OpenCAPI介面就是Google支持的技術之一,但他並未提到另兩個在去年發表的技術CCIX與GenZ,分別是開放性加速器介面,以及儲存級(storage-class)記憶體。

Google尋求更低成本的2.5D晶片堆疊

在封裝技術方面,Sabada表示將邏輯、記憶體、數位與類比裸晶結合在同一片基板上的2.5D晶片堆疊技術「令人振奮」,是一種實現異質晶片的「酷方法」;不過他也指出,該類技術的大量生產良率與成本還未達到令人滿意的程度。

AMD的繪圖處理器部門首席架構師最近也表達了類似的挫折(參考原文),該公司同樣正嘗試將晶片堆疊技術推向主流市場。

Sabada請求晶片產業高層加速各領域技術的創新,但他也理解,設計與生產先進晶片的複雜度與成本越來越高。「我們已經遭遇障礙,頻率的提升不是我們習慣的,基本上我們看到了單核心處理器性能的限制;」他指出,種種挑戰推動了往多核心處理器的轉移,但:「這在雲端環境中會是一個挑戰。」

Google在去年發表了張量處理單元(Tensorflow processing unit,TPU),將之視為未來潮流;Sabada表示:「我們已經邁入加速器時代…TPU只是你們將在接下來看到的這類元件案例之一。」他並指出,機器學習將會是雲端運算的關鍵驅動力,那是一個利用人工智慧的強大應用案例,也是Google許多雲端產品支援的能力。

編譯:Judith Cheng

(參考原文:Google Searches for Better Silicon,by Rick Merritt)

Source:EETimes

留言列表

留言列表