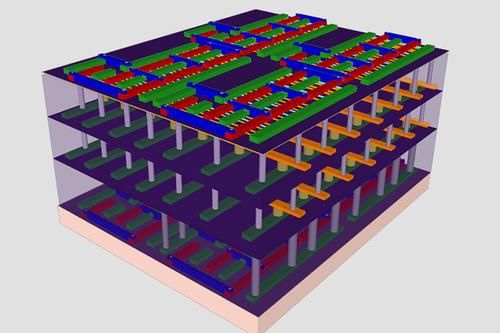

史丹佛大學展示的3D晶片以標準過孔方式連接4層電路,最底層是標準CMOS,最上層是碳奈米管邏輯電晶體,中間夾著2層RRAM。

(來源:Stanford, Mitra/Wong Lab)

美國奧勒岡州的新創公司BeSang將其專有製程技術授權給南韓的海力士半導體(SK Hynix Inc.),用於打造出無需透過 TSV 的真正 3D 技術。

美國史丹佛大學(Stanford University)的研究人員們在日前舉辦的2014年國際電子元件會議(IEDM)上展示了真正的 3D 晶片。大部份的 3D 晶片採用矽穿孔(TSV)的方式推疊不同的製造晶片,例如美光科技(Micron Technology)的混合記憶體立方體(HMC)推疊 DRAM 晶粒。

此外,總部設於美國奧勒岡州的新創公司BeSang將其專有製程技術授權給南韓的海力士半導體(SK Hynix Inc.),用於打造出無需透過 TSV 的真正 3D 技術。

然而,史丹佛大學所展示的是任何晶圓廠都能在標準的互補式金屬氧化物半導體(CMOS)上堆疊任何層數的邏輯與記憶體。在IEDM上,史丹佛大學在 CMOS 晶片上堆疊了2層的金屬氧化物電阻型隨機存取記憶體(PRAM),以及1層利用碳奈米管(CNT)作為電晶體通道的邏輯電路。

「對於使用傳統的跨層過孔而言, TSV 技術至關重要,但關鍵在於如果你想達到無法以 TSV 實現的極高能源密度效率之時,」史丹佛大學電子工程系教授Subhasish Mitra表示,「然而,我們能夠利用傳統過孔分別在各層之上順利地打造這些電路層,顯示我們的方法是可行的。」

史丹佛大學所採用的方法是在底層製造一種標準 CMOS 邏輯晶片,然後以二氧化矽絕緣體加以覆蓋,並且利用氬氣濺鍍蝕刻的方式使其平面化。在第二層的 RRAM 是由氮化鈦、氧化鉿(作為主動交換層)和鉑組成,然後在 CMOS 層上以200℃的溫度利用傳統 TSV進行製造(以免損壞 CMOS ),以實現互連。

標準的平面型CMOS晶片(圖左)透過TSV分別堆疊邏輯元件與記憶體於不同的結構;史丹佛大學的工程師為採用標準TSV的CMOS晶片上3層結構進行低溫製程,以實現更高密度。

(來源:Stanford, Mitra/Wong Lab)

然後,在經過 PRAM 以及另一層絕緣二氧化矽沈積後,另一層絕緣二氧化矽則沈積於 RRAM 之上並實現平面化。最上層則先以碳奈米管進行同向覆蓋,利用剝離(lift-off)方式形成石英晶片。為了實現足夠的密度,研究人員們進行13次的碳奈米管轉換方式。然後再用傳統的內層過孔(ILV)與微影技術,將碳奈米管製造於邏輯層上的電晶體通道中。

「我們可以利用這種技術製造出任意層數,」史丹佛大學教授H.S. Philip Wong說:「我們使用相當寬鬆的設計規則在學校的晶圓廠中製造這些電路層,但在其他的展示中則已證明我們的製程能一直微縮到現有採用過孔技術的20nm商用級。」

史丹佛大學的研究人員們還積極地展示在平面二氧化矽表面的碳奈米管性能,這是在平行碳奈米管上層利用標準圖形化技術,在場效電晶體(FET)中形成每通道約50個奈米管。研究人員們認為,這種碳奈米管電晶體由於具備較矽晶更高10倍的能效,因而可望在未來取代矽晶電晶體技術。

「我們想表達的是你可以先以標準矽晶 CMOS 作為底層,仍然能夠打造出 3D 晶片,但在未來,我們希望人們轉換成利用碳奈米管電晶體,因為他們的性能可進一步擴展到超越矽晶,這就是為什麼我們展示真正的碳奈米管電路,而不只是堆疊上的一個測試電晶體。」

研究團隊們強調,必須確保這種碳奈米層在溫度夠低的情況下製造,才不至於損壞 PRAM ,而在足夠的低溫下製造 PRAM ,才不會損壞到底層的 CMOS 晶片。數以千計的過孔實現各層的互連,才能使得這種碳奈米管場效電晶體(CNTFET)成為 PRAM 的理想選擇。

編譯:Susan Hong

(參考原文:True 3-D Chips Harness Nanotubes,by R. Colin Johnson)

Source:史丹佛大學

斯坦福大學工程師開發出的四層“多層芯片”原型。底層和頂層是邏輯晶體管,中間是兩層存儲芯片層。垂直的管子是納米級的電子“電梯”,連接邏輯層和存儲層,讓它們能一起工作解決問題。

左邊是目前的單層電路卡,邏輯與存儲芯片分隔在不同區,通過電線連接。就像城市街道,由於數據在邏輯區和存儲區來來回回地傳輸,常會產生擁堵。右邊是多層的邏輯芯片和存儲芯片,形成一種“摩天大樓”式的芯片,數據通過納米“電梯”實現立體傳輸,避免了擁堵。

今日視點 幾十年來,“更小、更快、更便宜”已成為推動電子設備發展的魔咒。最近,美國斯坦福大學工程師又給它增加了第四個——更高。在12月15日至17日美國舊金山召開的電氣和電子工程師協會(IEEE)國際電子設備大會上,斯坦福大學研究小組介紹了怎樣構建一種“多層”芯片,能大大提高目前電路卡上單層的邏輯和存儲芯片的性能。 電路卡就像繁忙的城市,在存儲芯片上存儲數據,通過邏輯芯片計算。當計算機繁忙時,連接邏輯芯片與存儲芯片的線路就會發生“數字交通擁堵”,而“多層”芯片能終結這種擁堵。

這種新方案能在存儲層上疊加邏輯層,緊密且互相連接,通過數千個納米級的電子“電梯”在各層之間運輸數據,將比目前單層邏輯芯片和存儲芯片間的連線速度更快,耗電更少。

三項突破

這項研究由斯坦福大學電學工程與計算機科學教授薩博哈西斯·米特拉和HS·菲利普·翁等人負責。據研究小組介紹,他們的創新研究取得了三項突破:

第一是製造晶體管的新技術,晶體管是微小的門,通過開關電流來代表1和0;

第二是新型的計算機存儲器,具有多層結構;

第三是把製造邏輯門和存儲器的新技術整合在一起,成為多層結構的新技術,這與以往的堆疊芯片完全不同。

“這項研究還在早期階段,但我們的設計和製造技術是可升級的。”米特拉說,“隨著今後的發展,這種結構將 會使計算機性能大大提高,超過現有任何計算機。”

翁說,這種芯片的原型已在去年的國際電子器件大會(IEDM)上展出過,顯示了怎樣把邏輯和存儲芯片結合到一種能大規模生產的三維結構上。可以說,這改變了芯片的範式。“有了這種新結構,電子製造業會把你手中的計算機變成強大的超級計算機。”

碳納米管造邏輯層

工程師幾十年前就已造出了矽芯片。但無論手機還是平板電腦都會發熱,放出熱量的大小也能顯示其內部問題。即使把它們關上,有時也會有電從矽晶體管中洩露。用戶會感覺到熱,對系統本身來說,這種洩露也會耗盡電池,浪費電力。研究人員正致力於解決這一難題,比如用碳納米管(CNT)晶體管。

碳納米管非常纖細,20億根才有一根頭髮粗細,所以漏電要比矽少得多。在米特拉和翁的第二篇會議論文中,介紹了他們是怎樣製造性能最高的碳納米管晶體管的。用以往的生產碳納米管的標準工藝,造出的納米管密度不夠緻密。他們攻克了這一難題,開發出一種靈活的技術,能把足夠多的碳納米管打包在足夠小的面積裡,以製造有用的芯片。

他們先在圓形石英晶片上用標準方法生產碳納米管,然後增加厚度到一定量,再用黏合法把整個碳納米管層從石英介質上剝離,放到矽晶片上。這種矽晶片就是他們多層芯片的基礎。

研究人員先要製造密度足夠大的碳納米管層,才能製造出高性能的邏輯設備。他們按這種工藝重複13次,在石英晶片上生長了一大堆碳納米管,然後用轉移技術剝離,把它們沉澱在矽晶片上。用這種簡捷的技術來固定,他們造出了一些迄今密度最高、性能最高的碳納米管。他們還證明了,在製造多層芯片時,能在超過一個邏輯層上實施這種技術。

“三明治式”存儲器

造出高性能的CNT晶體管層只是多層芯片的一部分,在每層CNT晶體管層上直接製作出存儲芯片也同樣重要。翁是製造這種存儲器的領導者。

翁設計的新型存儲器與目前的存儲器完全不同,不是以矽為基礎,而是用氮化鈦、二氧化鉿和鉑,構成一種金屬—氧化物—金屬的夾層結構,從一個方向通電會產生電阻,而反向通電則能導電。從電阻到導電狀態的改變,就是這種新存儲技術形成數字0和1的方式,所以它的名字就叫做電阻式隨機存取存儲器或RRAM。

RRAM比目前的存儲器耗電更少,在移動設備上使用能延長電池壽命。這種新的存儲技術也是製造多層芯片的關鍵,因為RRAM能以比矽存儲器更低的溫度製造。 多層互連

會議上展示的是斯坦福大學電學工程研究生馬克斯·修雷克和托尼·吳製造的四層芯片。製造RRAM和CNT晶體管層都是以低熱工藝為基礎,所以能在每層CNT邏輯芯片上直接製造存儲芯片層,在製造每層存儲芯片層時,能鑽數千個與下面邏輯層互相連通的小孔。在傳統的電路卡上,就是這種多層互連讓多層芯片能避免“交通擁堵”。

如果用傳統的矽基邏輯和存儲芯片,無法實現多層間的緊密互連。因為製造矽基存儲器要花太多熱量,大約要1000℃,這會讓下面的邏輯芯片融化。

以往也有人研究堆疊式矽芯片,這會節約空間,但無法避免數據“交通擁堵”。因為每層芯片都要獨立製造,並用電線連接——這仍然傾向於擁堵,與研究小組設計的“納米電梯”是完全不同的。

來源:科技日報

留言列表

留言列表