當論及在不同處理器或記憶體之間提高晶片之間的傳輸流量時,光子學是一個熱門的話題。截至目前為止,微波導、光調變器、輸出耦合光閘與光探測器均已成功進行整合了,但要設計理想的微米級光源仍十分具有挑戰性。

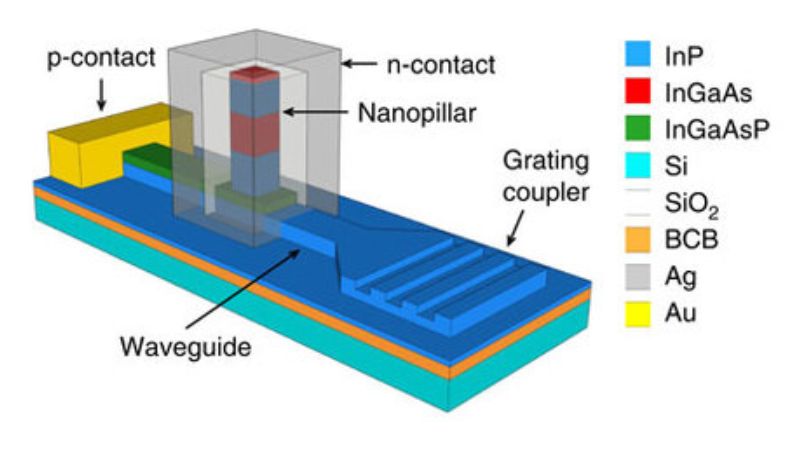

荷蘭愛因霍芬科技大學(Eindhoven University of Technology)的研究人員在最近一期的《自然通訊》(Nature Communications)期刊中發表有關「晶片上波導耦合奈米柱金屬腔發光二極體」(Waveguide-coupled nanopillar metal-cavity light-emitting diodes on silicon)的最新研究。研究人員展示一種接合至矽基板的奈米級LED層堆疊,並可耦合至磷化銦(InP)薄膜波導形成光閘耦合器。

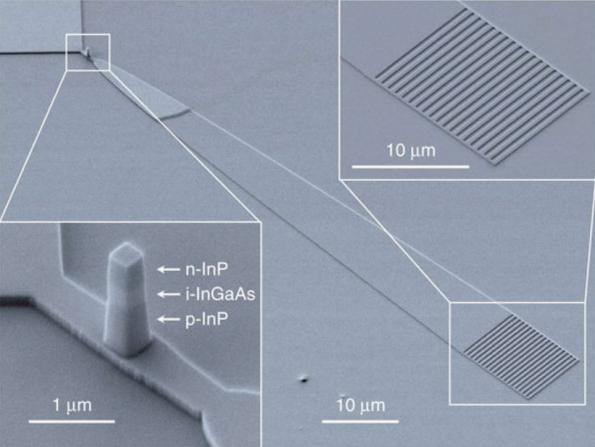

新式奈米級LED (nano-LED)的掃描式電子顯微鏡圖(SEM)顯示在金屬化之前的製造元件結構。奈米柱LED位於連接至光閘耦合器的波導頂部

這種nano-LED採用次微米級的奈米柱形狀,其效率可較前一代元件更高1,000倍,在室溫下的輸出功率僅幾奈瓦(nW),相形之下,先前的研究結果約為皮瓦(pW)級輸出功率。根據該研究論文顯示,這種元件能夠展現相當高的外部量子效率(室溫分別為10^−4~10^−2,以及9.5K)。

而在低溫時,研究人員發佈的功率級為50nW,相當於在1Gb/s速率下每位元傳輸超過400個光子,這一數字「遠遠高於理想接收器的散粒雜訊(shot-noise)極限靈敏度。」該元件作業於電信波長(1.55μm),能以頻率高達5GHz的脈衝波形產生器進行調變。

矽基板上的奈米柱狀LED示意圖。從頂層到底層的堆疊分別是:n-InGaAs(100 nm)/n-InP(350 nm)/InGaAs(350 nm)/p-InP(600 nm)/p-nGaAsP(200 nm)/InP(250 nm)/SiO 2/BCB/SiO2/Si

研究人員表示,「由於短距離互連的損耗低,以及整合接收器技術持續進展,這一功率級可望以超精巧的光源實現晶片內部的資料傳輸。」

研究人員還開發了一種表面鈍化方法,能夠進一步為nano-LED提高100倍的效率,同時透過改善歐姆接觸(ohmic contact)進一步降低功耗。

編譯:Susan Hong

(參考原文:nano-LED could support multi-Gbit/s on chip traffic,by Julien Happich)

Source:EETimes

留言列表

留言列表