在這個典型的無線架構中,所有數位功能可整合在單一元件中。

蜂巢式網路業者設法透過全新傳輸介面、傳輸頻率、更高頻寬以及增加天線的數量和更多無線基地台提升網路密度,因此須要大幅降低設備的成本。另外,這些業者為降低營運成本,也需要更高運作效率和網路整合度的設備。無線基礎設備製造商為提供可以符合不同要求的設備,皆在尋求更高整合度、更佳效能和靈活度高的解決方案,並且同時降低功耗和成本。

整合度是降低整體設備成本的關鍵,然而這必須依賴可提升功率放大器效率的高階數位演算法來降低各項運作成本,其中一項最常用的演算法是數位預失真(DPD)。由於設備的配置愈來愈複雜,因此提升設備運作效率是一項很大的挑戰。藉由先進長程演進計畫(LTE-Advanced)傳輸技術,無線傳輸頻寬可達到100MHz,如果廠商試圖用連續頻譜配置結合多種傳輸介面,頻寬甚至可以更高。主動天線陣列(AAA)和支援多重輸入/輸出(MIMO)技術的遠端無線單元(RRU)所需的演算法對頻寬的要求愈來愈高。本文將探討業界完全可編程系統單晶片(All Programmable SoC)元件如何為目前和未來的數位預失真系統提升效能增益,同時也可為設備廠商提供充裕的可編程能力、低成本和低功耗,並加快產品上市時程。

建置蜂巢式無線網路

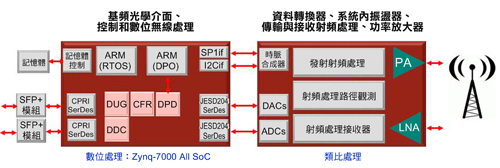

業界完全可編程SoC元件結合高效能可編程邏輯(PL)架構,其中包含序列式收發器(SERDES)和整合硬體處理子系統(PS)的數位訊號處理器(DSP)模塊。這個硬體處理子系統內含一個雙核心安謀國際(ARM)Cortex-A9處理器、浮點運算單元(FPU)和NEON多媒體加速器及一系列豐富的周邊功能,包括通用異步收發器(UART)、串列周邊介面(SPI)、內部整合電路(I2C)、乙太網路(Ethernet)和記憶體控制器等完整無線傳輸所需的周邊功能。有別於外部通用處理器或DSP,可編程邏輯和硬體處理子系統間的介面有大量連結,因此其頻寬可以非常高;但如要用獨立式解決方案處理這些連結,卻不可行。此外,完全可編程SoC元件還包含硬體和軟體陣列,因此可在單一晶片內建置遠端無線單元所需的功能,如圖1所示。

可編程邏輯中豐富的DSP資源可用於建置數位上行轉換(DUC)、數位下行轉換(DDC)、峰波因數抑制(CFR)與數位預失真(DPD)等數位訊號處理功能。此外,SERDES可支援9.8bit/s的通用型公共射頻介面(CPRI)和12.5bit/s JESD204B,分別用於連接基頻和資料轉換器。

硬體處理子系統同時支援對稱式多重處理技術(SMP)和非對稱式多重處理技術(AMP)。在這個案例中預定會採用非對稱式多重處理模式,因為其中一顆ARM Cortex-A9處理器被用於建置基板層級的控制功能,例如訊息終止、排程、設定等級以及警示執行(裸機或更有可能是如Linux等作業系統)。而另一顆ARM Cortex-A9處理器則用以建置部分數位預失真演算法,因為數位預失真演算法並不保證整體都是硬體的解決方案。

數位預失真可藉由擴大其線性範圍提升功率放大器效率;當驅動放大器進一步增加輸出功率時,即可提升運作效率,而靜態功耗會相對維持正常。數位預失真為擴充其線性範圍,會使用放大器中的類比反饋路徑和大量數位處理功能計算放大器的逆向非線性係數。然後利用這些係數預先校正與驅動功率放大器的傳輸訊號,最終可增加放大器的線性範圍。

數位預失真是一個封閉迴路系統,其會擷取先前的傳輸訊號來決定放大器與這些傳輸訊號的傳輸方法。數位預失真的第一個任務是要讓放大器與先前的傳輸訊號達成一致,這個過程會在一個校準模塊中進行。在執行任何演算法運算前,系統會用記憶體來校準資料;資料一旦妥善校準後即可運用自動相關矩陣運算(AMC)和係數運算(CC)演算法,建立代表功率放大器逆向非線性係數的最近值。一旦產出係數後,資料路徑前置失真器即運用資料預校準被傳輸到功率放大器的訊號。

資料來源:新電子

留言列表

留言列表