初創企業X-Celeprint在拉斯維加斯舉辦的ECTC會議上提交了4篇論文,主題是關於他們的微轉印技術(μTP技術)、工藝流程以及該技術的微電子應用。μTP技術作為一項先進的微裝配技術,可以使數百個小型(最適宜尺寸為亞毫米級)器件在同一時間內精確移動。

X-Celeprint是XTRION NV的全資子公司,XTRION NV旗下還包括著名的X-Fab公司。他們從塞木普銳斯公司(Semprius)獲得技術授權,並且在2014年初開始正式運營。微轉印技術的最初發明者為伊利諾大學香檳分校的John Rogers教授,隨後在塞木普銳斯公司獲得進一步發展。

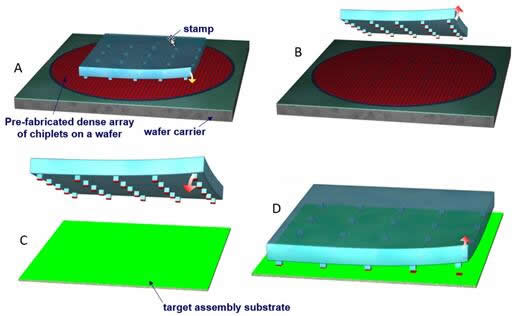

用最簡單的語言來描述微轉印技術,就是使用彈性印模(stamp)結合高精度運動控制打印頭,有選擇地拾取(pick-up)微型器件的大陣列,並將其打印(放置)到替換基板上。首先,在“源”晶圓上製作微型器件(芯片),然後通過移除半導體電路下面的犧牲層獲得“釋放”。隨後,一個微結構彈性印模(與“源”晶圓匹配)被用於拾取微型器件,並將這些微型器件打印(放置)在目標基板上。

通過改變打印頭的速度,可以選擇性地調整彈性印模和被打印器件之間的黏附力,最終控制裝配工藝。當印模移動較快時,黏附力變得很大,得以“拾取”被打印元件,讓它們脫離基板;相反,當印模遠離鍵合界面且移動較慢時,黏附力變得很小,被打印元件便會“脫離”,然後“打印”在接收面上。

印模通過設計,可以實現單次拾取和打印操作,轉移成千上萬個分立元器件,因此這項工藝流程可以實現大規模並行處理。例如,240平方微米的芯片被放置在間距為250 um的晶圓上,需要把芯片“打印”(放置)到間距為2 mm的新表面上,印模上的末端(參考下圖轉印印模)就會被製作成2 mm的間距,然後從晶圓上拾取1、8、16等芯片,一次打印完成後再回來拾取2、9、17等芯片。

微轉印工藝流程:圖A:彈性印模接近晶圓;圖B:彈性印模拾起芯片;圖C:彈性印模接近基板;圖D:印模將芯片“印刷”(放置)在基板上

該技術已經在眾多“可印刷”微型器件中得到驗證,包括激光、LED、太陽能電池和各種IC材料(矽、砷化鎵、磷化銦、氮化鎵和包括金剛石在內的介電薄膜)的集成電路。

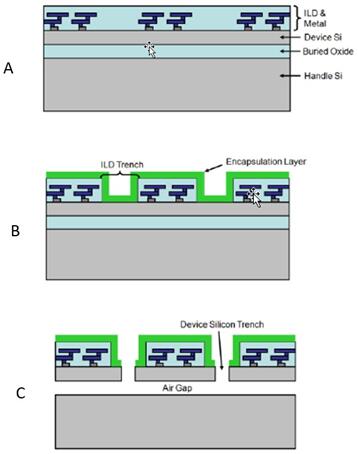

大多數情況下,需要轉印的器件首先會從“源”晶圓上得到釋放,該方法利用了器件層下方的犧牲釋放層。對於矽器件,絕緣體上矽(SOI)晶圓代表方便、隨時可用的“源”晶圓。利用商業化的SOI CMOS加工工藝處理5 um器件矽層和1 um埋氧層(BOx)來製作電路。

按照CMOS加工工藝,一段溝槽截至圍繞器件周圍的器件矽層,封裝層被施加在SOI CMOS“源”晶圓上,用來在隨後的BOx層刻蝕中,保護ILD和佈線層。SOI CMOS晶圓通過刻蝕工藝,用HF(氟化氫)去除器件下方的BOx層,器件最終從晶圓中完全脫離出來,並通過器件層中的“栓繩”來進行位置固定。在轉印期間,“栓繩”可以通過可控的方式斷裂或切開。犧牲層刻蝕工藝完成後,當IC芯片可以轉印時,封裝層將會被移除。

製作轉印用器件:圖A:晶圓代工所以採用的SOI晶圓;B:溝槽和封裝層構造;圖C:器件矽層開槽,移除埋氧層

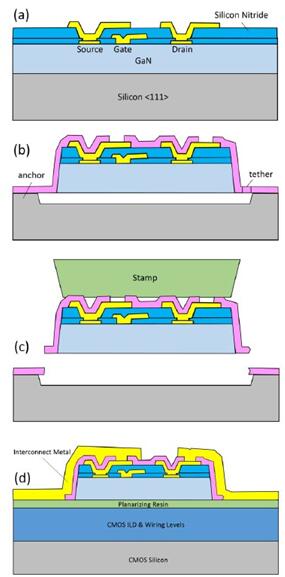

2016年ECTC會議上,論文《微轉印技術助力微型氮化鎵晶體管的異質整合》的作者,來自X-Fab的Ralf Lerner詳細描述了構造GaN芯片的工藝流程。

GaN HEMTs異質整合工藝流程:圖a:在矽晶圓上製作晶體管;圖b:器件被隔離、鈍化、切底;圖c:器件被抬取黏附在彈性印模上;圖d:器件被打印到CMOS晶圓上,並利用薄膜鋁跡線與CMOS晶圓連接

氮化鎵晶體管在直徑為100mm的矽晶圓<111>上製作而成。通過穿過器件層,向下直至矽基板的反應離子刻蝕(RIE),實現單個器件的分離。在該步驟中使用了二氧化矽硬掩膜。通過等離子體增強化學氣相沉積法(PECVD)將600 nm的氮化矽層沉積。氮化矽層可以鈍化器件側壁,也可以用於錨定和“栓繩”結構的形成。

氮化鎵芯片隨後被轉移到矽基CMOS晶圓上。印刷前,在CMOS晶圓上施以一層半導體薄膜級平坦化樹脂,微轉印完成後,底層樹脂在175 °C時被固化。接下去進行鎢化鈦和鋁的金屬疊層濺射沉積,隨後進行減厚濕法刻蝕,最終形成器件的連接。轉印的GaN HEMT芯片厚度大約為5μm,濺射沉積鋁在器件側壁的佈線中起到了有效作用。

相互連接的GaN HEMT:圖A:鋁佈線分佈在轉印的GaN HEMT側壁上;圖B:展開圖

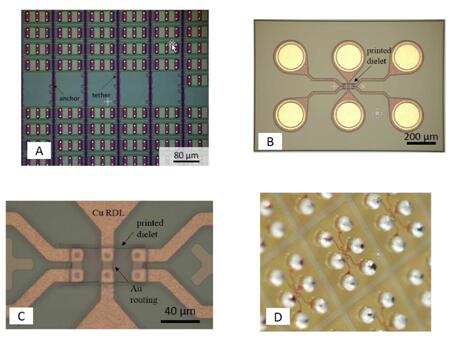

在論文《微轉印技術助力微型器件的扇出型封裝》中,來自X-Celeprint和RTI Int的研究員們描述了不需要注模材料,製作亞毫米器件扇出封裝的高通量策略。微轉印技術被用來組裝重新裝配的晶圓器件(尺寸80um x 40um,擁有重分佈金屬和6個觸點封裝的芯片),面朝上,印刷(放置)在200 mm的晶圓上。裝配完成後,晶圓器件將經過標準化晶圓級再分配和凸塊工藝處理。最終,200 mm晶圓上的扇出型封裝器件的尺寸為1.4mm x 1.0mm,器件上有6個250 μm焊接凸塊。最終的扇出型封裝將在FR4測試板上組裝並回焊。

因為封裝中沒有使用任何注模材料,因此不需要模壓成型器件所使用的芯片模具。

該轉印工藝良率預估高達99.7%,每30秒就能轉印300個芯片。

使用微轉印技術製作晶圓級封裝芯片:圖A:部分“拾取”後的芯片“源”晶圓;圖B:焊球置放前完整的扇出型封裝;圖C:特寫;圖D :最終的扇出型晶圓級封裝

兩塊PCB板上填充了60顆芯片,每顆芯片都經過JESD環境(-40°C 到125°C)下的熱循環測試。沒有一顆芯片顯現出超過0.2歐姆的平均熱阻變化。

資料來源:X-Celeprint

留言列表

留言列表