在舊金山舉行的2016年國際電子元件會議上,比利時研究組織imec發佈首個整合垂直堆疊閘極全環(gate-all-around,GAA)矽奈米線金屬氧化物半導體場效電晶體(MOSFET)的互補式金屬氧化物半導體(CMOS)。

IMEC把這項工作描述為「促進GAA奈米線MOSFET開發所取得的突破性成果,將可望在未來技術節點中接替鰭式場效電晶體(FinFET)」。這個整合方案中的關鍵是雙重工作功能的金屬閘極,它可使n型和p型元件閾值電壓得以匹配。另外,IMEC還研究這種新架構對固有靜電放電(ESD)性能的影響,並提出一種靜電放電保護二極體。

imec的報告繼續說道:「GAA奈米電晶體將可望在7奈米及更先進技術節點中成為接替FinFET的候選產品。它們可提供最佳的靜電控制效能,並支援最終的CMOS元件尺寸縮減,在半導體發展橫向配置中,它們是目前主流FinFET技術的自然延伸。在這種配置中,可透過垂直堆疊多個水平奈米線來最大化每個覆蓋區的驅動電流。今年早些時候,IMEC的科學家展示基於垂直堆疊的8奈米直徑矽奈米線的GAA FET,這些元件具有卓越的靜電控制能力,不過是針對n-FET和p-FET分開製造的。」

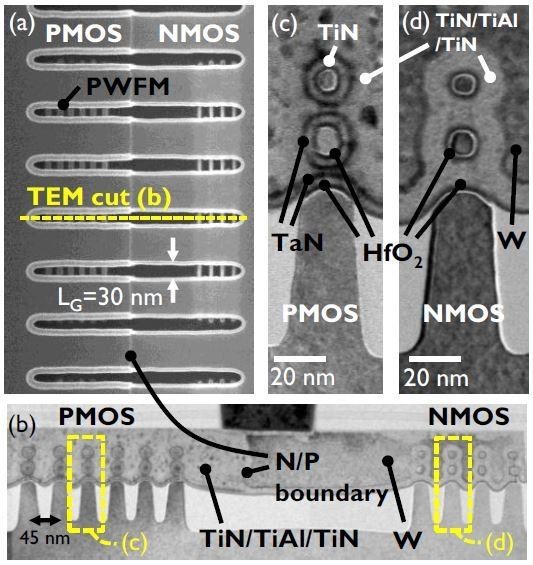

本次大會上,IMEC報告的是整合垂直堆疊的GAA矽奈米線MOSFET的CMOS,針對n型和p型元件都有匹配的閾值電壓。在這個製程步驟中,p型工作功能金屬(p-type work function metal ,PWFM)被沉積在所有元件的閘極溝道中,隨後有選擇地將PWFM蝕刻到n-FET的HfO2中,最後沉積n型工作功能金屬。對nMOS和pMOS元件的匹配閾值電壓(VT,SAT=0.35V)的觀察有效地驗證雙重工作功能金屬的整合方案。

圖1 (a)在PWFM從n-FET蝕刻後的掃描電鏡(SEM)影像頂視圖,(b)~(d)在工序最後階段的p-FET和n-FET的透射電鏡(TEM)影像橫截面圖(LG=30nm)。

imec還研究了這種新的元件架構對固有靜電放電性能的影響。他們推薦了兩種不同的靜電放電保護二極體:一種是閘極結構定義的二極體(閘控二極體);一種是淺溝道隔離定義的二極體(STI二極體)。STI二極體是一種比較好的靜電放電保護元件,具有卓越的故障電流(It2)與寄生電容(C)比值。測量結果和TCAD模擬也顯示,與大批量FinFET二極體相比,可以維持基於GAA奈米線二極體中的ESD性能。

「GAA奈米線電晶體支持最終CMOS元件尺寸縮減,與其他縮減方案相比,增加的複雜度很低。」IMEC邏輯元件與整合總監Dan Mocuta表示,「針對矽GAA CMOS技術推薦的這種整合方案,以及靜電放電保護方面的結果,是朝著實現這些7奈米及更先進技術節點發展道路上取得的重要成就。未來的工作將專注於進一步優化個別製程步驟,比如結點和奈米線形成的協同優化。」

imec對先進邏輯縮減的研究是與IMEC核心CMOS計畫中的重要合作夥伴一起合作。這些合作夥伴包括GlobalFoundries、華為、美光(Micron)、英特爾(Intel)、高通(Qualcomm)、三星(Samsung)、SK Hynix、索尼(Sony)和台積電等。

Source:IEEE

留言列表

留言列表