VLT記憶體單元:帶有寫入輔助的PMOS電晶體的閘流體

垂直分層閘流體(Vertical Layered Thyristor;VLT),是Kilopass研發出的新型記憶體單元,能夠顯著降低動態隨機存取記憶體(DRAM)的成本和複雜性。這是一種靜態的記憶體單元,無需刷新操作;相容於現有晶圓廠的製造設備,也無需任何新的材料或製程。

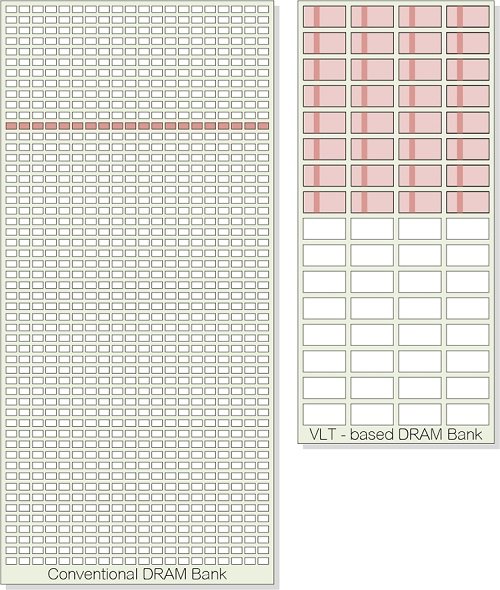

相較於一般的DRAM,VLT記憶體陣列能節約高達45%的成本;這是因為它具有更小的VLT記憶體單元,以及驅動更長行與列的能力,使其得以大幅提升記憶體陣列效率。然而,想要發揮VLT的優勢,就必須在依據產業標準發展的成熟DRAM市場展開設計與製造,才能確保相容於不同供應商的記憶體產品。

目前,基於VLT技術的記憶體已經具備與現有「第四代低功耗雙倍數據速率」(LPDDR4)規格完全相容的能力。VLT記憶體組(bank)可以模擬傳統DRAM的bank,並相容於其時脈;在設計VLT電路時,設計者可以選擇連接標準DDR控制器,或是成本較低的簡化版控制器。如果使用標準控制器,由於不需要刷新,VLT記憶體將會忽略刷新序列。系統的其他部份則會將VLT DRAM視為通用DRAM,因而無需任何改變。

傳統DRAM記憶體單元

為了顯示如何使用VLT記憶體單元構造LPDDR4記憶體,首先回顧一下傳統DRAM以及LPDDR4的工作方式。熟悉DRAM者或許對其有所瞭解,但實際運用上還是有些微差異,在此先定義一些準則與術語以便於理解。

DRAM作業的許多方面取決於其電容儲存單元。首先,電容的漏電特性導致了刷新的必要性;其次,儲存單元的基本作業方式之一是讀取,它會影響如何組織記憶體的其他方面。

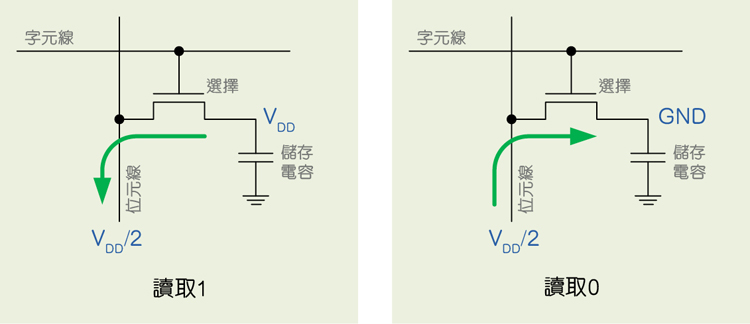

圖1顯示電容儲存單元的原理圖,左右圖分別代表了讀取1和讀取0時。電路透過「電荷分配」(charge sharing)偵測記憶體位元值。位元線(bitline)首先被預充電到一個在0和1之間的電壓值,然後透過打開讀數電晶體來選擇一個記憶體單元,使電荷可以在位元線與記憶體單元間流動。如果位元線電壓高於記憶體單元,那麼負電荷就會從記憶體單元流出到位元線上;而如果位元線的電壓低於記憶體,那麼負電荷就會從位元線流進記憶體單元。

圖1:傳統電容式DRAM記憶體單元的電荷分配原理 (圖中綠色箭頭所示為電流,與負電荷流動的方向相反)

這種電荷轉移改變了位元線上的電壓,透過感測與鎖存得到最終讀取數值。然而,在儲存電容中失去或取得的電荷,改變了節點上原有的電荷,這意味著讀取的過程是破壞性的。因此,在每一次讀取之後,都必須透過回寫操作恢復記憶體單元中的電荷。

LPDDR4

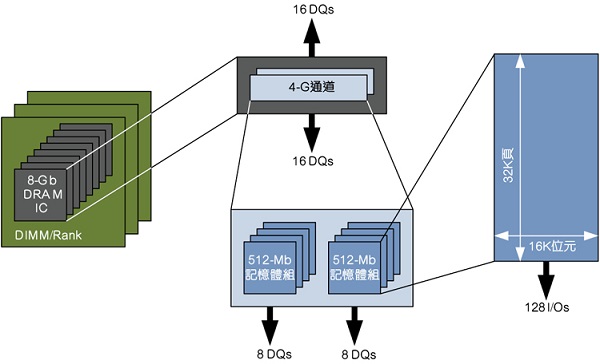

LPDDR4標準是第四代雙倍數據速率(DDR) DRAM的低功耗版本標準,透過整體架構定義了個別記憶體晶片的高層級結構,以及如何安排雙列直插式記憶體模組(DIMM)。

分析DRAM的方式一般有兩種:理論上,剖析其實體細節;實際上,則著眼於其晶片陣列特性。本文首先探討第一種邏輯觀點,因為所有的實體佈局都必須分解為相同的邏輯結構,因而能夠從中瞭解傳統DRAM和LVT途徑如何實現邏輯功能。

LPDDR4記憶體晶片擁有8Gb的儲存容量,通常由兩個4Gb的獨立通道共同組成。每通道擁有8個記憶體組,每一記憶體組包括32K儲存頁(page),每頁有16K位元,而使記憶體組的總容量達到512Mb。

圖2:典型的DRAM架構和層級

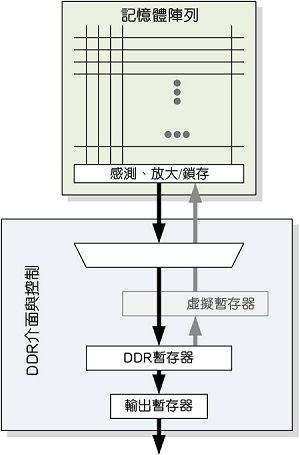

一個完整的LPDDR4記憶體晶片包括兩個高層級單元:記憶體陣列和DDR介面。有些部份的操作會影響到記憶體陣列;另一部份則會影響介面。DDR介面可以同時與記憶體陣列以及外部系統進行通訊。

圖3:LPDDR4的邏輯組織架構,圖中將儲存陣列和DDR介面分開。箭頭代表一次讀取操作以及回寫

圖3說明了這種關係,即DDR暫存器作為外部系統和記憶體陣列之間的主介面。而在讀取資料時,陣列資料會先被載入DDR暫存器中;進行寫入作業時,所需的資料會先從外部寫入暫存器中。

由於讀取傳統DRAM陣列內容可能破壞原有資料,每一次讀取後都必須進行回寫作業,以恢復原有值。在進行讀取後,DDR暫存器的內容被複製到「隱藏暫存器」(Shadow Register)中。當外部系統讀取DDR暫存器中的資料時,隱藏暫存器負責將資料回寫到所選頁,以恢復原有數值。同樣地,當寫入資料時,DDR暫存器的資料會被傳輸到隱藏暫存器中等待寫入;而在執行寫入作業時,DDR暫存器就可以載入新的資料。

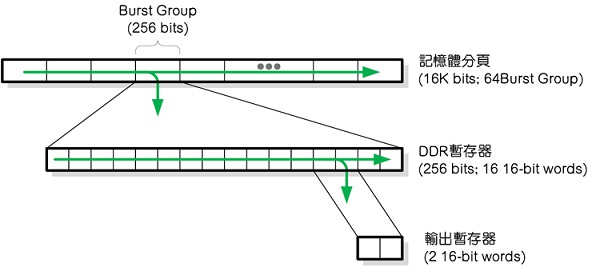

讀取記憶體分頁資料涉及一連串的活動,類似於兩個巢式的軟體DO迴路(Do loop)。每一分頁記憶體被分成由許多256位元組成、成批(burst)讀取的記憶體群組,因此,一組16K位元分頁就有64個burst記憶體群組,依序讀取完整的記憶體頁,這類似於外部DO迴路。

![]()

圖4:記憶體分頁由分批依序讀取的記憶體群組構成;每一批burst群組均依據16個連續的16位元傳送到I/O

每個突發傳輸組被載入256位元的DDR暫存器中,該暫存器被分為16個16位元字,並依序讀取其內容,為每一個時脈邊緣提供每一個16位字。這種操作方式則如同內部DO迴路。

每一行的位址(RAS)負責選擇分頁。同時,每一列的位址(CAS)選擇突發傳輸組,並設置從DDR暫存器中開始讀取的字元,因而不必從DDR暫存器的左側開始讀取。

值得注意的是,在隱藏暫存器執行回寫、讀取或寫入DDR暫存器中原先載入資料的同時,DDR暫存器已經開始從儲存陣列中讀取資料或從外部載入所寫資料了。

LPDDR的運作

LPDDR4功能本質上包含四項基本操作:啟動、讀取、寫入和預充電。這些操作的其他變異形式,如突發讀取/寫入和自動預充電等,可能構成一個更長的指令清單,但並不至於帶來新的技術挑戰。此外,它還添加了刷新、訓練和模式暫存器作業等維護性指令,以因應複雜的操作命令。

這些基本的操作簡要介紹如下: 啟動: 在記憶體陣列中選擇特定字元線(wordline),即可「開啟」一個分頁。該分頁上的內容將會被感測到並進行鎖存,然後保持開啟以用於在讀取作業時進行回寫,或在「讀取-修改-寫入」作業時被再次寫入。

讀取: 開啟讀取資料序列,每個burst記憶體群組的資料會從感測放大鎖存中被載入到DDR暫存器中。緊接著DDR暫存器開始依序讀取,每次讀取一個16bit字。同時,晶片透過隱藏暫存器在仍保持開啟狀態的分頁上進行回寫。

寫入: 資料被載入DDR暫存器,每次一個16位元字。資料隨後被轉移到隱藏暫存器中,待分頁開啟時寫入資料。當進行寫入時,DDR暫存器可依需要同時載入新的256位元資料,等待下一次寫入。

預充電: 在最後一個burst記憶體群組被讀取或寫入後,記憶體陣列必須為下一次操作做好準備。在寫入情況下,必須等待一個寫入恢復延遲,以確保最後的burst群組可在繼續其他操作前被成功寫入。這時,開啟的分頁已被關閉,使位元線能夠自由浮動,並重新充電回到先前提到的VDD/2電位。

值得注意的是,只有啟動操作才涉及記憶體陣列感測;讀取操作只涉及在鎖存感測資料與DDR暫存器之間傳輸資料,以及讀取DDR暫存器的數值。

根據所需的操作序列不同,有些DDR的時序可能極其複雜。但如果相鄰讀取操作發生在不同記憶體組的資料之間,則可大幅簡化時序。因為在從下一個記憶體組中讀取資料之前,不必在原有的記憶體組中等待回寫和預充電。時序控制最困難的是來自同一記憶體組的連續讀寫。

實現記憶體陣列:MAT

理論上,儘管一個記憶體組的邏輯容量可能達到32K行與16K列,但以現有技術而言,現實上並不可能製造出這樣的記憶體陣列。這是因為:

- 驅動器在選擇分頁時的驅動能力有限;在性能符合規格要求的前提下,只有一定數量的選定電晶體可以被驅動。

- 感測放大只能支援有限數量的儲存單元。如果儲存單元的數量太多,由於電荷分配造成電壓變化減小,而被雜訊淹沒。

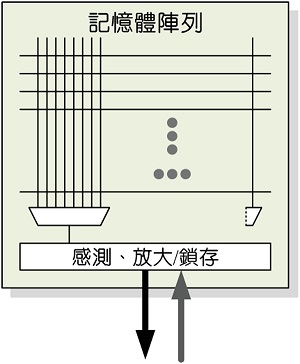

因此,為了確保記憶體晶片可靠且易於製造,每一種記憶體應用都存在不同程度的實體尺寸限制。達到這種上限的記憶體陣列被稱作「記憶體陣列片」(memory array tile;MAT)。每個MAT都是功能齊全的陣列,本身包含字元線和位元線的解碼以及感測放大器。

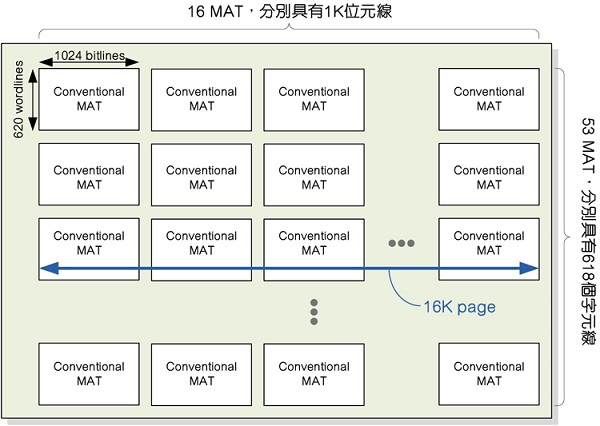

以一種採用2x-nm製程節點的一般DRAM MAT為例,其位元線和字元線的規模分別達到1,024條和620條。字元線的數量並不是2的整數次方,這帶來了一些解碼方面的挑戰。該晶片或許只用了最後的幾個MAT,但這是一個可以忽略的晶片建置細節。

透過打造一個16×53大小的MAT陣列,可為具有這一尺寸的記憶體組實現總共848個MAT。一個完整分頁整合一行MAT的記憶體單元:當開啟一個分頁時,同時啟動同一行有MAT記憶體單元上相應的字元線。

![]()

圖5:傳統DRAM的實體佈局

在瞭解了這些背景知識後,接下來將討論全新的Kilopass記憶體單元,以及它如何打造與此相同的儲存組。

VLT記憶體單元

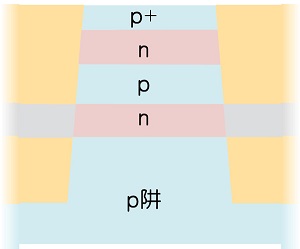

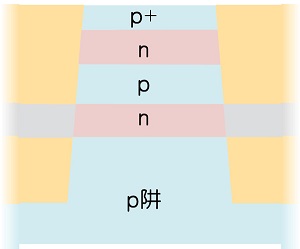

Kilopasss的全新記憶體單元基於一種垂直分佈的閘流體(也被稱為半導體控制整流器,或SCR)。這種採取pnpn結構的堆疊建構於一個p-阱上,可帶走來自底部n型層的任何空洞。

圖6:VLT記憶體單元:帶有寫入輔助的PMOS電晶體的閘流體

在淺溝槽隔離(STI)結構中植入一個埋入式字元線,使底部的n層連接到一個字元。埋入式字元線與外部銅金屬M1層字元線透過具有較大電阻的金屬鎢實現連接,因而可以製造比傳統DRAM更長的字元線。

由於感測機制並非採用電荷分配,使感測放大器可承受更長的位元線。因此,這種技術可以支援高達2Kbit寬、4Kbit深或總共8M位元的MAT——遠大於傳統的DRAM MAT。採用更少片較大型MAT拼接成的記憶體晶片較採用多片小尺寸MAT的花費更低,因而可使VLT記憶體的陣列效率達到77%,相形之下,同樣採用2x-nm節點的傳統DRAM效率只有64%。

以VLT記憶體單元打造LPDDR4記憶體

MAT容量增大後,LPDDR4記憶體組就可以用更少的MAT組成。單純按照位元數計算,基於VLT技術的記憶體組將包含64個MAT,相形之下,傳統DRAM的記憶體組需要配置848個更小的MAT。不過,接下來的問題就是如何最有效配置這些MAT。

一種配置方式是每個MAT都帶有512個支援4K位元線的感測放大器,這意味著每個感測放大器都有多工器用於在8條位元線中進行選擇。其中,多工器的選擇基於CAS位址;進一步針對圖3的記憶體陣列進行修改後,新的原理圖如下:

圖7:為VLT記憶體添加位元線多工器

因此,對於每個被選定的分頁,每個MAT中只有八分之一的位元線會被選擇,這與普通DRAM實現方式中所有位元線都被選中的情況不同。但在傳統DRAM中並不可能實現這種更高效率的感測放大器使用方式,因為所有的位元線都必須被讀取,以實現回寫的目的。由於VLT讀取並不是破壞性的,因而無需回寫操作,且多個記憶體單元可共用感測放大器。

另一個問題是如何在一個MAT實體陣列中配置這些MAT。基於VLT MAT的靈活性,實體上配置這些MAT可以不必與邏輯上的配置完全吻合。只要妥善安排各匯流排的路徑,任何形式的配置都是可能的。舉例來說,一個記憶體組可被配置為4×16個MAT陣列,同時傳輸理論上與傳統LPDDR4相同的資料。

圖8說明傳統DRAM和VLT技術在記憶體分頁選擇上有什麼不同:傳統DRAM選擇一行中的所有MAT,而VLT則從中選擇了一個4×8的MAT區塊。

![]()

圖8:記憶體分頁選擇,其中被選定的MAT是紅色的。傳統DRAM透過行來選擇分頁,而VLT DRAM則以單元區塊選擇分頁

由VLT製造的LPDDR4,在外部操作上與傳統LPDDR4完全相同。內部操作可能有所差異,例如不必再回寫和預充電,但這並不會影響DDR控制器;如果滿足了VLT的時序要求,其記憶體的邏輯組織方式與傳統DDR完全一致。

免除刷新

VLT記憶體單元最明顯的優點之一就是不需要刷新。不過,刷新已經成為DRAM作業的一部份了;無論記憶體處於閒置狀態或是被接通,都必須進行刷新操作,以避免資料丟失。

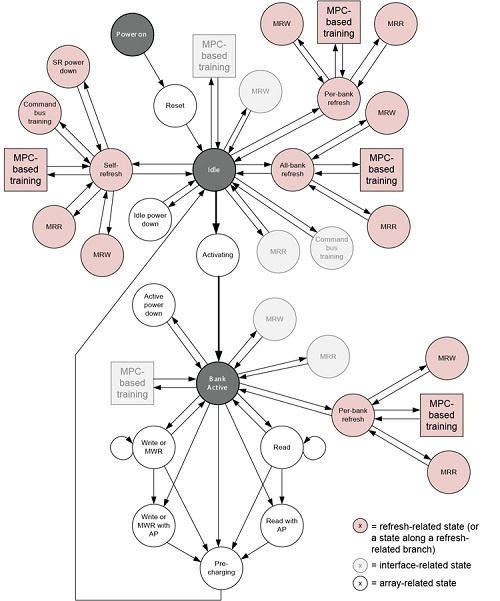

完整的DDR控制器狀態機說明了刷新對於運作的影響,如圖9所示,所有紅色的狀態都與刷新或者基於刷新的分支相關;而使用了VLT技術,這些狀態都是冗餘的,而且能夠被消除。

圖9:傳統DRAM建置的LPDDR4狀態原理圖,與刷新有關的狀態以及與基於刷新的有關分支狀態都被標註為紅色,標註為灰色的狀態則與介面相關

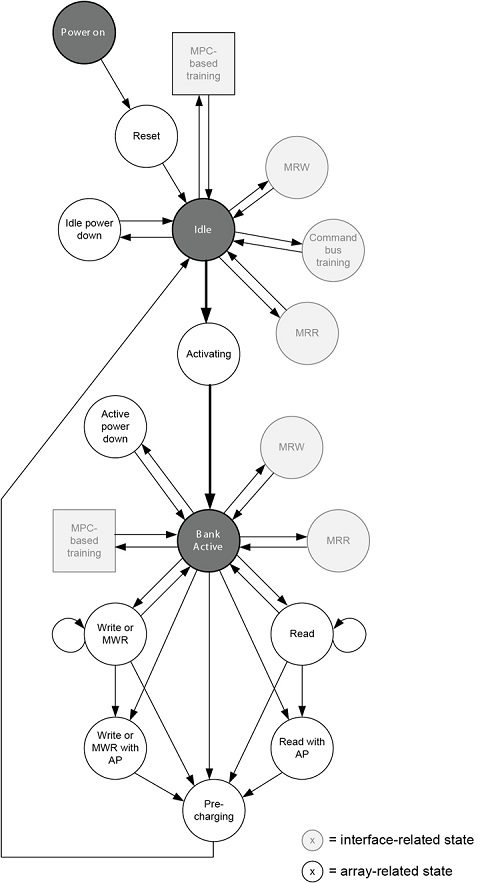

圖10則是一種簡化的狀態機,其中與刷新有關的狀態都已經移除了。在設計基於VLT的記憶體時,設計者可以選擇現有的DDR控制器,因應那些不需要的狀態加以調整;也可以設計最佳化的DDR控制器,省去所有與刷新相關的電路——這種方法將佔用更小的晶片面積,以及降低功耗。無論選擇哪一種控制器,都不會影響其他系統與記憶體晶片的互動。

圖10:移除與刷新相關狀態後的LPDDR4狀態原理圖

結語

VLT記憶體單元可以打造一種比普通DRAM記憶體單元成本更少、功耗更低的記憶體,目前VLT記憶體晶片已能與現有的LPDDR4記憶體完全相容了。透過適當設計架構、命令以及時序,VLT記憶體晶片就能與傳統記憶體晶片無差別地應用在實際系統上。

基於VLT的記憶體陣列採用一個可在內部作業處理差異的介面,使其得以與標準的LPDDR4控制器配合使用。換句話說,設計一款免刷新的LPDDR4控制器,使其仍具備完整的控制器功能以支援外部介面,並確保現有驅動器都能繼續正常作業,而只是在內部忽略與刷新有關的操作,將有助於大幅節省成本,以及降低功耗。

Source:EETIME

留言列表

留言列表